Tugas 9 : Latches, FF and Timer Oleh : [Ikram] [2103015119]

Latches, Flip-Flop and Pewaktu (Timer)

Dengan cara yang sama bahwa gerbang adalah blok bangunan sirkuit kombinatorial, kait dan sandal jepit adalah blok bangunan sirkuit sekuensial. Sementara gerbang harus dibuat langsung dari transistor, kait dapat dibuat dari gerbang, dan sandal jepit dapat dibuat dari kait. Fakta ini akan membuatnya lebih mudah untuk memahami kait dan sandal jepit.

Baik kait maupun flip-flop adalah elemen rangkaian yang outputnya tidak hanya bergantung pada input saat ini, tetapi juga pada input dan output sebelumnya. Perbedaan antara latch dan flip-flop adalah bahwa latch tidak memiliki sinyal clock, sedangkan flip-flop selalu memiliki sinyal clock.

Latches

Bagaimana kita bisa membuat rangkaian dari gerbang yang tidak kombinatorial? Jawabannya adalah umpan balik, yang berarti bahwa kita membuat loop dalam diagram rangkaian sehingga nilai keluaran bergantung, secara tidak langsung, pada dirinya sendiri. Jika umpan balik tersebut positif maka rangkaian cenderung memiliki keadaan stabil, dan jika negatif rangkaian akan cenderung berosilasi.

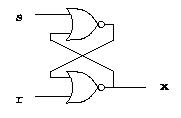

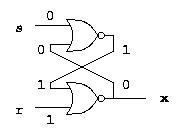

Kait memiliki umpan balik positif. Berikut adalah contoh kait sederhana :

Kait ini disebut SR-latch, yang merupakan singkatan dari set dan reset.

Tidak praktis untuk menggunakan metode yang telah kami gunakan untuk menggambarkan rangkaian kombinatorial untuk menggambarkan perilaku SR-latch. Kemudian, kami akan menunjukkan metode untuk menggambarkan flip-flop dan sirkuit sekuensial clock. Untuk saat ini, kami hanya mengandalkan intuisi kami untuk menggambarkan cara kerja kait.

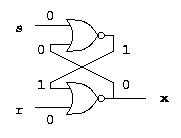

SR-latch dimaksudkan untuk memiliki paling banyak satu inputnya sama dengan 1 setiap saat. Ketika kedua inputnya adalah 0, ia memiliki dua status stabil yang berbeda. Entah x adalah 0, dalam hal ini kami memiliki nilai sinyal berikut :

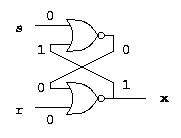

atau x adalah 1, dalam hal ini kita memiliki nilai sinyal berikut :

Nilai sebenarnya tergantung pada riwayat nilai input seperti yang akan kami tunjukkan selanjutnya.

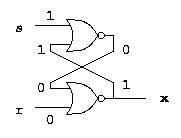

Sekarang anggaplah s adalah 1 (dan oleh karena itu r adalah 0 karena kami mengizinkan paling banyak satu input menjadi 1 setiap saat). Kami mendapatkan nilai sinyal berikut :

1 pada input s memastikan output gerbang nor atas adalah 0, dan dua 0 pada input gerbang nor bawah memastikan output x adalah 1.

Sekarang anggaplah input s berubah dari 1 ke 0, sedangkan input r tetap pada 0. Input kedua dari gerbang nor atas adalah 1, jadi transisi dari 1 ke 0 dari input s, tidak membuat perbedaan. Keluaran x tetap pada 1. Dalam hal ini, jika masukan s dan r keduanya 0, hanya ada satu kemungkinan keadaan stabil, keadaan yang memberikan nilai x 1.

Sebaliknya, misalkan r adalah 1 (dan oleh karena itu s adalah 0 karena kami mengizinkan paling banyak satu input menjadi 1 setiap saat). Kami mendapatkan nilai sinyal berikut:

d

d https://onlinelearning.uhamka.ac.id/my/

Komentar

Posting Komentar